www.afm-iournal.de

# A Surface Tailoring Method of Ultrathin Polymer Gate **Dielectrics for Organic Transistors: Improved Device** Performance and the Thermal Stability Thereof

Hyejeong Seong, Jieung Baek, Kwanyong Pak, and Sung Gap Im\*

Tailoring the surface of the dielectric layer is of critical importance to form a good interface with the following channel layer for organic thin film transistors (OTFTs). Here, a simple surface treatment method is applied onto an ultrathin (<15 nm) organosilicon-based dielectric layer via the initiated chemical vapor deposition (iCVD) to make it compatible with organic semiconductors without degrading its insulating property. A molecular-thin oxide capping layer is formed on a 15 nm thick poly(1,3,5-trimetyl-1,3,5-trivinyl cyclotrisiloxane) (pV3D3) by a brief oxygen plasma treatment. The capping layer greatly enhances the thermal stability of the dielectrics, without degrading the original mechanical flexibility and insulating performance of the dielectrics. Moreover, the surface silanol functionalities formed by the plasma treatment can also be utilized for the surface modification with silane compounds. The surface-modified dielectrics are applied to fabricate low-voltage operating (<5 V) pentacene-based OTFTs. The highest field-effect mobility of the device with the surface-treated 15 nm thick pV3D3 is 0.59 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, which is improved up to two times compared to the TFT with the pristine pV3D3. It is believed that the simple surface treatment method can widely extend the applicability of the highly robust, ultrathin, and flexible pV3D3 gate dielectrics to design the surface of the dielectrics to match well various kinds of organic semiconductors.

### 1. Introduction

Organic thin film transistors (OTFTs) have drawn a considerable research interest due to their unique advantages including cost-effectiveness, low process temperature suitable for flexible substrates, mechanical flexibility, and lightweight. In last decade, to harness these benefits of OTFTs, various kinds of electronic devices (e.g., displays, sensors, radio frequency identification (RFID) tags) had been fabricated using OTFTs. [1,2] For further extended application of OTFTs to low-power-consuming

H. Seong, J. Baek, K. Pak, Prof. S. G. Im Department of Chemical and Biomolecular Engineering & Graphene Research Center KI for Nanocentury Korea Advanced Institute of Science and Technology 291 Daehak-ro, Yuseong-gu, Daejeon 305-701, Republic of Korea

E-mail: sgim@kaist.ac.kr

DOI: 10.1002/adfm.201500952

and portable devices, the device performance must be substantially improved. To this end, high-performance organic gate dielectric layers with high mechanical stability and large-area processability are urgently requested.[1]

However, OTFTs made of polymer gate dielectrics are suffering from high operating voltage, typically exceeding 20 V,[3,4] due to the gate dielectrics with the thickness often greater than 100 nm to ensure low gate leakage current.[4] Thermally crosslinked polymers including poly(4vinylphenol) (PVP),[5] Cytop,[6] benzocyclobutene (BCB),[7] and polyimides (PIs)[8] have been adopted for gate dielectrics, but only few of them could successfully reduce the operating voltage of OTFTs down to 10 V by reducing the thickness of dielectric layer. Moreover, the high annealing temperature required to induce the crosslinking of polymer gate dielectrics is also problematic, which may cause damage to OTFTs and limit their application to thermally vulnerable substrates.

Besides reducing the operating voltage of OTFTs, controlling the interface

between dielectric and semiconductor is another critical factor to optimize the performance of OTFTs. [9,10] Applying selfassembled monolayers (SAMs)<sup>[10]</sup> or plasma treatment<sup>[11]</sup> had been widely applied to optimize the film morphology of semiconductors on the surface of gate dielectrics. However, most of these SAM treatment procedures require specific surface coupling reaction, and had been applied mostly onto inorganic dielectric layers rather than polymer dielectrics, mostly due to the lack of target surface functionalities on most of the polymer dielectrics and/or a reliable, damage-free coupling reaction applicable onto the polymer dielectrics.

Recently, we have proposed initiated chemical vapor deposition (iCVD) as a new deposition method to form ultrathin (<10 nm) crosslinked polymer dielectrics with high density.[12] iCVD is a well-established dry process, which can deposit highly pure polymer thin films in mild process temperature (10-40 °C) and pressure (in the order of 100 mTorr). [13] Especially, an organosilicon polymer, poly(1,3,5-trivinyl-1,3,5-trimethyl cyclotrisiloxane) (pV3D3), exhibited an extremely low leakage current (less than 10<sup>-9</sup> A cm<sup>-2</sup> at 3 MV cm<sup>-1</sup>) even with ultralow thickness (≈6 nm), and chemical/mechanical robustness. Nevertheless,

ADVANCED FUNCTIONAL MATERIALS

www.afm-journal.de

surface modification of such a thin layer of pV3D3 to tailor the interface for various semiconductors has not yet been demonstrated so far.

Here, we formed a molecular thin  ${\rm SiO}_x$  capping layer on the top of 15 nm thick pV3D3 dielectrics by introducing a simple oxygen plasma treatment to modify the surface of pV3D3. It is well known that oxygen plasma treatment or ultraviolet/ozone (UVO) irradiation can produce  ${\rm SiO}_x$  skin layers on crosslinked polysiloxanes, [14] and the same approach was also applicable to the organosilicon pV3D3 films. The insulating property of  ${\rm O}_2$  plasma-treated pV3D3 was maintained even after the thermal exposure of 280 °C up to 3.5 h in ambient air, confirming the improved thermal and environmental stability of ultrathin pV3D3 dielectrics. Furthermore, the  ${\rm O}_2$  plasma-treated pV3D3 thin film exhibited high flexibility up to tensile strain of 3.3%, which is far superior than previously reported SAM/AlOx-based dielectric layer, whose yield strain was 1.5%. [15]

The surface silanol (—Si—OH) groups formed by the plasma treatment on the  $\mathrm{SiO}_x$  capping layer could further be utilized for the purpose of surface modification platform using silane-based SAM treatment. Various kinds of silane compounds could successfully change the surface characteristics of pV3D3 dielectric layer. The exquisite tunability of surface functionality could further be harnessed to optimize the interfacial compatibility with the following channel layer. As an example, pentacene-based OTFTs with various kinds of silane-treated pV3D3

were fabricated and a substantial improvement of OTFT performance was achieved. The simple, but versatile method to form oxide capping layer could significantly improve the device performance by controlling the surface functionality, as well as increasing the thermal stability of the ultrathin pV3D3 dielectric layer.

#### 2. Results and Discussion

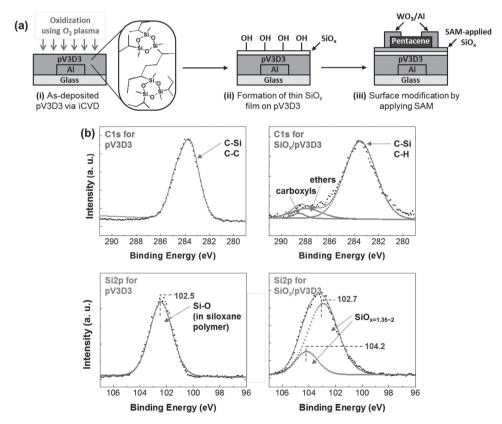

A vapor-phase polymerization method, iCVD was used for the deposition of pV3D3 and a densely crosslinked polymer film was formed, as illustrated in Figure S1 (Supporting Information). pV3D3 is composed of core hexagonal Si-O rings surrounded by aliphatic carbon backbone chains. Because the pV3D3 is composed of Si-O rings, a brief O2 plasma exposure (50 W for 15 s) (Figure 1a-i) can efficiently remove the surface carbon components in pV3D3 layer to leave a thin SiO, capping layer on pV3D3. Especially, the top surface of SiO<sub>x</sub> capping layer consists of hydrophilic silanol groups (Si-OH), which can serve as reactive sites with silazanes and silanes to form a stable Si-O-Si linkage (Figure 1 a-ii).[16] This silanol coupling reaction can further be used as a tool for surface modification of pV3D3 dielectric layer. Unlike the most of carbonbased polymer dielectrics where the same silane treatment will only form an unstable Si-O-C bonding, silane treatment on

**Figure 1.** a) Schematic of the preparation steps of surface-modified pV3D3 dielectric layers. i) and ii) indicates the formation of nanometer-thick oxide capping layer with surface silanol (—Si—OH) functionalities via O<sub>2</sub> plasma treatment. iii) Modified pV3D3 dielectric layer with various SAM materials including HMDS, OTS, and PFTS are applied to fabricate pentacene TFTs. b) High-resolution XPS spectra of C1s (top) and Si2p (bottom) for untreated (left) and O<sub>2</sub> plasma-treated (right) pV3D3, respectively.

www.afm-journal.de

www.MaterialsViews.com

plasma-treated pV3D3 can modify the surface using SAM with highly reliable Si—O—Si linkage. The SAM materials used in this work to tailor the surface of pV3D3 dielectrics were hexamethyldisilazane (HMDS),<sup>[10]</sup> octadecyltrimethoxysilane (OTS),<sup>[17]</sup> and trichloro(1*H*, 1*H*, 2*H*, 2*H*-pefluorooctyl)silane (PFTS),<sup>[18]</sup> which are most commonly chosen reagents for the surface treatment of gate dielectrics, especially in pentacene-based TFTs on well-established SiO<sub>2</sub> dielectric layer (Figure 1a-iii).<sup>[19]</sup>

First, X-ray photoelectron spectroscopy (XPS) was performed to explore the surface components of plasma-treated pV3D3. The XPS survey scans and high-resolution scans of C1s and Si2p spectra for the pV3D3 before and after the plasma treatment were compared, as shown in Figure 1b and Figure S2 (Supporting Information). The XPS survey and high-resolution C1s scan indicate that the pristine pV3D3 contains considerable amount of carbon in C-Si and C-C bonds. On the other hand, after the plasma treatment, overall surface composition of C was significantly reduced (Figure S2, Supporting Information) and the peaks related to the oxidized carbons were newly emerged (Figure 1b, top right). In particular, the Si-O peak in Si2p XPS spectra of untreated pV3D3 was slightly shifted to the higher binding energy after the plasma treatment (Figure 1b, bottom). The continuous shift of the main peak towards higher binding energies indicates the increase of O content in the SiO<sub>x</sub> layer.<sup>[20]</sup>

Atomic force microscopy (AFM) images and XPS depth profiles of the pristine and  $O_2$  plasma-treated pV3D3 are also shown in **Figure 2**. The surface became hydrophilic instantly after the plasma treatment, but the surface roughness and

**Figure 2.** AFM images of a) untreated and b)  $O_2$  plasma-treated pV3D3 surfaces. Inset images indicate the water contact angle of each surface. Root-mean-square roughness ( $R_q$ ) of each surface was also noted in the image. The XPS depth profiling of c) untreated and d)  $O_2$  plasma-treated pV3D3, respectively.

topography remained unchanged apparently even after the O<sub>2</sub> plasma treatment (Figure 2a,b). This observation indicates that the plasma treatment condition applied in this work was gentle enough not to cause any crack or winkle on the dielectric surface, which could originate from the difference in the elastic modulus between the formed SiO<sub>x</sub> skin layer and the pV3D3 layer underneath.<sup>[21]</sup> In the XPS depth profiling in Figure 2c, concentrations of Si, C, and O were constant along the perpendicular direction. This confirms the uniform composition of pV3D3 formed via the iCVD process, which is fully consistent with the previous observation.<sup>[12]</sup> On the other hand, unlike the untreated pV3D3, surface of O2 plasma-treated pV3D3 showed significantly increased O concentration up to 60% and lowered C concentration of 11.8%, as shown in Figure 2d, illustrating the selective etching of carbon components in pV3D3 layer by the applied oxygen plasma. The sharp change of C and O concentration near the surface indicates that the oxidation of pV3D3 by the oxygen plasma is strictly confined only to the very surface layer. The concentration of Si remained almost constant throughout the depth profile, indicating that the plasma oxidation process did not etch the Si component out, unlike the case of C. A slight increase at the surface of Si concentration was observed at the skin oxide layers, most likely due to the relatively heavy etching of C component to form SiO<sub>x</sub> layer. The estimated thickness of SiO<sub>x</sub> layer on pV3D3 by the XPS depth profiling was no larger than 3 nm, which matches well with the optically measured thickness obtained from ellipsometry (data not shown).

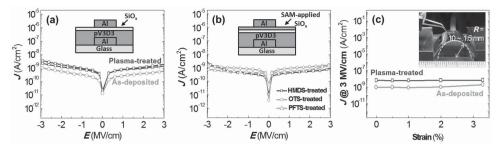

To monitor the effect of O2 plasma treatment on pV3D3 to the insulating properties of pV3D3 dielectrics, a metal-insulator-metal (MIM) device was fabricated with O2 plasma-treated 15 nm thick pV3D3 layer. The leakage current density (1) of  $O_2$  plasma-treated pV3D3 film was lower than  $3 \times 10^{-9}$  A cm<sup>-2</sup> in a range of  $\pm$  3 MV cm<sup>-1</sup>, confirming that the plasma treatment did not damage the insulating property of bulk pV3D3 film (in Figure 3a). The insulating properties of various SAMtreated pV3D3 layers were also monitored using MIM devices with 15 nm thick pV3D3 layers whose surfaces were modified with HMDS, OTS, and PFTS. Even with the extremely thin dielectrics, the low I of pV3D3 was unchanged after the HMDS, OTS, and PFTS treatment (Figure 3b), which clearly indicates that the 15 nm thick pV3D3 is thermally and chemically robust enough to withstand the SAM treatment procedure requiring up to 150 °C of annealing temperature. The surface modification of pV3D3 dielectric layer with the SAM layers was confirmed by water contact angle (WCA) analysis. The WCA of bare pV3D3 layer changed from 91° to 71°, 95°, and 106° after treating with HMDS, OTS, and PFTS, respectively (in the inset figure in Figure S3, Supporting Information). The surface roughnesses of modified layers were also sufficiently low (rootmean square (RMS) roughness ( $R_q$ ) of < 0.4 nm), as shown in the AFM images in Figure S3 (Supporting Information). Furthermore, the pV3D3 film retained its own flexibility after the plasma treatment, which can be seen in Figure 3c. Both of the MIMs on polyethylene naphthalate (PEN) substrates fabricated with as-deposited and plasma-treated pV3D3 thin film exhibited virtually unchanged I upon to a radius of curvature (R) as small as 1.5 mm for a tensile stress, which corresponds to a tensile strain of 3.3%.

www.afm-journal.de

**Figure 3.** a) Leakage current density (*J*) vs electric field (*E*) of as-deposited and plasma-treated 15 nm thick pV3D3. b) *J* vs *E* characteristics of MIM devices with 15 nm thick pV3D3 dielectric layers modified with various SAMs of HMDS, OTS, and PFTS. c) The *J* measured at 3 MV cm<sup>-1</sup> for various tensile strain values for as-deposited and plasma-treated 30 nm thick pV3D3. The inset photographs show the set-ups for bending test of MIM devices.

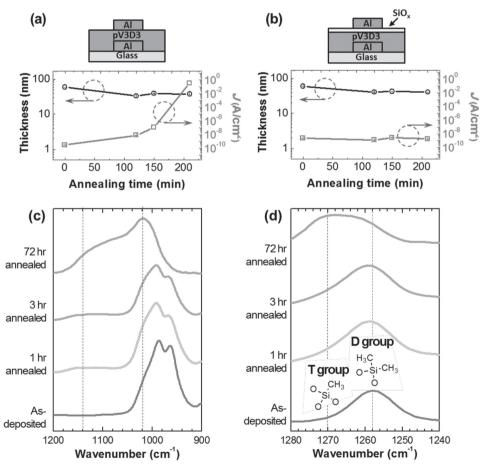

To investigate the long-term thermal stability of plasmatreated pV3D3 layer, the layer was exposed to the temperature of 280 °C. The J of MIM devices with plasma-treated pV3D3 layer was as low as  $2 \times 10^{-8}$  A cm<sup>-2</sup> at 3 MV cm<sup>-1</sup> even after a 3.5-hr thermal annealing at 280 °C (in **Figure 4**b), which suggests the plasma-treated layer is thermally stable enough to withstand further surface modification process with SAMs. The

improved thermal stability is likely originated from the existence of robust oxide skin layer, which could substantially stabilize the chain movement of unconverted pV3D3 layer underneath the oxide skin layer. For comparison, thermal stability of the pristine pV3D3 layer was investigated with the same thermal treatment condition applied above. With the lapse of exposure time, the insulating property of pV3D3 was severely

Figure 4. Change of thickness with the increased of annealing time with a temperature of 280 °C. a) as-deposited pV3D3 and b) plasma-treated pV3D3 with SiO<sub>x</sub> capping layer. c) FTIR spectra of as-deposited pV3D3 and films annealed at 150 °C for 1, 3, and 72 h in the range showing the Si—O—Si stretching vibration. Broadening and peak shift from 900–1050 cm<sup>-1</sup> to 1000–1200 cm<sup>-1</sup> indicates the ring opening event of pV3D3. d) FT-IR spectra of as-deposited pV3D3 and films annealed at 150 °C for 1, 3, and 72 h for the Si—CH<sub>3</sub> bonding region. Peaks at 1260 and 1270 cm<sup>-1</sup> correspond to  $O_2Si(CH_3)_2$  (D-group) and  $O_3Si(CH_3)$  (T-group), respectively. Formation of T-group means a crosslinking structure was emerged, in which silicon is bound to three network-forming oxygen atoms.

www.MaterialsViews.com

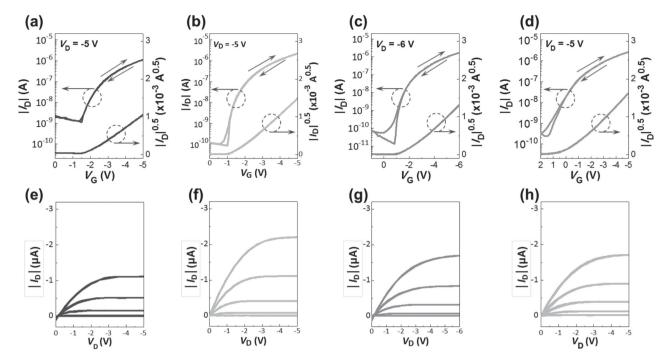

Figure 5. a-d) Transfer and e-h) output characteristics of pentacene TFTs fabricated with pV3D3 and SAM-treated pV3D3 as a dielectric layer: a,e) untreated, b,f) HMDS-treated, c,g) OTS-treated, and d,h) PFTS-treated pV3D3, respectively.

degraded (Figure 4a). Note that no noticeable loss of film thickness was detected from the both of thermally annealed pristine and plasma-treated pV3D3 layer (Figure 4a,b), which is fully consistent with the thermogravimetic analysis (TGA) of pV3D3 in Figure S4 (Supporting Information), indicating no major mass loss in bulk of pV3D3 up to 280 °C. However, damage to the bulk pV3D3 film with a thermal stress above 280 °C was unavoidable even with the plasma-treated pV3D3 layer, due to the severe mass loss above this temperature, as shown in Figure S4 (Supporting Information).

To figure out the reason why the insulating property was degraded without the mass loss, Fourier transform infrared (FTIR) analysis of as-deposited pV3D3 and thermally annealed pV3D3 films with several thermal stress time intervals at 150 °C was performed. Figure 4c demonstrates the evolution of the Si—O bonding nature of the annealed pV3D3 films. The thermal annealing for more than 1 h induced an increase of the peak intensity at the 1140 cm<sup>-1</sup> in the FTIR spectrum. The evolution of the FTIR peak shape for the thermally annealed pV3D3 layer in this wavenumber is quite similar to that of change in linear polysiloxane, such as polydimethylsiloxane (PDMS), which strongly infers that the breakage of siloxane ring in pV3D3 was occurred to form linear siloxane by the applied thermal stress.

Further increase of the annealing time up to 72 h resulted in a large peak shift in the FTIR spectra, featured by the formation of a broad peak at around 1140 cm $^{-1}$  and the shift of major peak from 950–1000 to 1020 cm $^{-1}$  (Figure 4c). The broad peak around 1000–1200 cm $^{-1}$  and the peak at 1020 cm $^{-1}$  indicate the formation of a silsesquioxane (SQ)-like cage structure [23] and suboxide (—O—Si—O—)Si— structure, [24] respectively, illustrating that the siloxane ring structure in pV3D3 layer was damaged to form a suboxide inorganic layer. [25] The formation of

cage and suboxide structure in pV3D3 film is most likely due to the reaction between oxygen and reactive sites in the linearized pV3D3 by the thermal damage. Dramatic change was also found in Si—CH<sub>3</sub> bonding peak of the pV3D3 film annealed for 72 h (Figure 4d). The peaks near the 1260 and 1270 cm<sup>-1</sup> correspond to Si—CH<sub>3</sub> bending mode in O<sub>2</sub>Si(CH<sub>3</sub>)<sub>2</sub> (D-group) and C—H<sub>3</sub> bending mode in O<sub>3</sub>Si(CH<sub>3</sub>) (T-group), respectively.<sup>[26]</sup> D-group linkage is dominant in as-deposited pV3D3. As the annealing time increased up to 72 h, a significant fraction of the silicon bound in D-group in the as-deposited polymer was converted to T-group, which also strongly supports the aforementioned observation of SQ-like cage structure in the annealed pV3D3 film

Finally, the pV3D3 thin layers whose surface was modified with HMDS, OTS, and PFTS were adopted as dielectric layers for the fabrication of pentacene TFTs. Figure 5 shows the device performance of the pentacene TFTs with HMDS, OTS, and PFTS-treated pV3D3 as gate dielectric layers, respectively. A pentacene TFT with pristine pV3D3 layer was also fabricated as a control device. All the relevant electrical parameters extracted from the graphs in Figure 5 were summarized in Table 1. The OTFT with HMDS-treated pV3D3 in Figure 5b showed a significantly lowered threshold voltage  $(V_T)$  close to zero, and an improved on-off ratio of >105, far larger than that of control pentacene TFT (Figure 5a). The field-effect mobility  $(\mu_{\text{FET}})$  of device with HMDS surface treatment was reached up to 0.59 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, which was improved up to two times compared to the mobility of the pentacene TFT with pristine pV3D3 dielectric layer (0.33 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>). Furthermore, the subthreshold swing (S.S.) of the device with HMDS-treated pV3D3 was also improved to 0.216 V/decade. The on-off ratio,  $V_{\rm T}$ , and S.S. of the OTFT with OTS-modified pV3D3 were also

www.afm-iournal.de

Table 1. Statistical data of fabricated TFT devices.

| Dielectric         | Water contact<br>angle [°] | Total thickness<br>(T <sub>i</sub> )* [nm] | Capacitance $(C_i)$ * $[nF cm^{-2}]$ | On–off ratio $(I_{on}/I_{off})$ | Threshold voltage $(V_T)^*[V]$ | Field-effect mobility $(\mu_{FET})$ * [cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ] | Subthreshold swing (S. S.)*[V/decade] |

|--------------------|----------------------------|--------------------------------------------|--------------------------------------|---------------------------------|--------------------------------|------------------------------------------------------------------------------------------|---------------------------------------|

| As-deposited pV3D3 | 91                         | 12.1 ± 0.2                                 | $161.5 \pm 3.0$                      | >103                            | $-1.5 \pm 0.01$                | $0.33 \pm 0.01$                                                                          | 0.463 ± 0.076                         |

| HMDS-treated pV3D3 | 71                         | $13.7 \pm 0.2$                             | $142.3 \pm 2.5$                      | >104                            | $-0.9\pm0.01$                  | $0.59 \pm 0.03$                                                                          | $0.216 \pm 0.020$                     |

| OTS-treated pV3D3  | 95                         | $12.3\pm0.6$                               | $158.4\pm7.6$                        | >105                            | $-0.2\pm0.06$                  | $0.31 \pm 0.01$                                                                          | $0.350 \pm 0.011$                     |

| PFTS-treated pV3D3 | 106                        | $13.0 \pm 0.3$                             | $150.4\pm3.5$                        | >104                            | $1.1 \pm 0.29$                 | $0.44\pm0.03$                                                                            | $0.646 \pm 0.069$                     |

<sup>\*5</sup> TFTs in the substrate were measured for the statistical analysis.

substantially improved, compared to the performance of the device with pristine pV3D3.

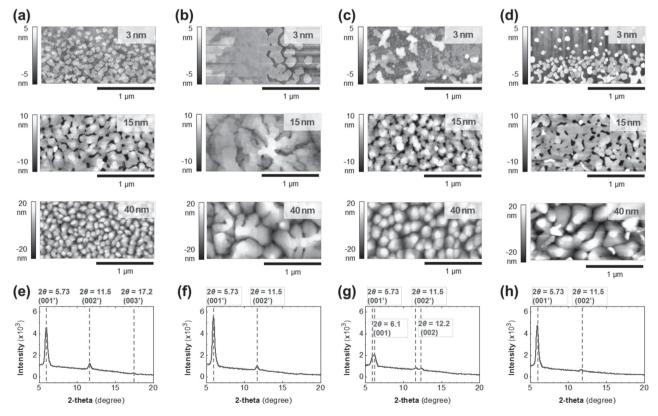

The  $\mu_{\text{FET}}$  and other device performances of the OTFTs were highly dependent upon the surface morphology of the pentacene deposited on the SAM-treated pV3D3 layers. [9,10,19] To investigate the reason why the substantial improvement in device performance was achieved by the surface treatment, 3 nm thick (corresponds to 2 monolayers (MLs) of pentacene), 15 nm thick, and 40 nm thick pentacene grains on each surface was analyzed via AFM (in Figure 6a-d). On the hydrophobic as-deposited pV3D3 surface, a small, faceted pentacene seed layer was formed (Figure 6a, top). The small seed layer resulted in the final grain of pentacene on the as-deposited pV3D3 with the average grain size of about 100 nm. On the contrary, the surface modification of pV3D3 layer led to a drastic morphological change on the pentacene film. A layered pentacene grain structure was clearly exhibited with the average grain size of 1 µm on a slightly more hydrophilic HMDS-treated pV3D3 (water contact angle of 71°) due to the large, faceted seed layer with high surface coverage. Unlike the case of HMDS-treated pV3D3, seed layers with dendritic island-like morphology were found on the OTS-treated surface. The dendritic morphology is reported to represent a divergent polycrystalline growth initiated from a common nucleation points. [27] Because of the morphological complexity of the dendrite, the pentacene layer will have a higher chance to form intra-grain boundaries within the island domains, [28] which can explain why the OTS-treated TFTs displayed the lowest mobility among the devices. This observation is also well consistent with the previous reports on the SAM-treated SiO2 dielectrics, where the seed layer and the resultant grain size of semiconductor were closely related with the device performance in that the increased number of grain boundaries can cause a decrease of

Figure 6. AFM images of thermally evaporated pentacene films (3 to 50 nm) on different dielectric surfaces: a) as-deposited, b) HMDS-treated, c) OTS-treated, and d) PFTS-treated pV3D3. (e) to (h) are corresponding XRD spectra of 40 nm thick pentacene on each surface.

www.afm-journal.de

Makrials Views

www.MaterialsViews.com

mobility because the grain boundaries will act as trap sites in charge transport.<sup>[29]</sup>

Furthermore, XRD spectra of 40 nm thick pentacene on each surface were also obtained (Figure 6e–h) to further elucidate the change of device performance by the SAM treatment on pV3D3. From all pentacene layers, a series of (00k') XRD patterns was detected, indicating a highly textured phase, which is called as a "thin film phase." Forming the "thin film phase" is highly advantageous to the charge transport in pentacene.<sup>[30]</sup> The intensity of (001') lines also reflects the amount of "thin film phase" in pentacene crystal. The highest intensity was observed for the pentacene on HMDS-treated surface, while the OTS-treated

surface exhibited the lowest intensity. In addition, the (00*k*) XRD patterns are observed from the pentacene layer on OTS-treated surface, which is a second phase of the pentacene, called as a "triclinic crystal bulk phase." The series of (00*k*) XRD patterns only observed in OTS-treated pV3D3 indicates the disordered crystalline structure in the pentacene grain, which will negatively affect to the charge transport in pentacene.

In the case of TFT with PFTS-treated pV3D3 (in Figure 5d), the on-off ratio, S.S., and  $\mu_{\text{FET}}$  were also improved from the device with pristine pV3D3. The seed layer of pentacene on the PFTS-treated pV3D3 was smaller than that on OTS-treated pV3D3, but compared to the morphology of the 15 nm thick pentacene films on OTS-treated surfaces, where the pentacene started forming smaller grains, more uniform pentacene layers were formed on PFTS-treated pV3D3, leading to a huge difference in final pentacene grains and further affecting to the device performance. It is worthy of noting that a significant  $V_T$ shift was observed from the device with PFTS-treated pV3D3. Previous report indicated that SAMs with fluorine are known to accumulate holes in the transistor channel, which can explain the shifted V<sub>T</sub> in TFT with PFTS-treated pV3D3 dielectric layer.[18,31] The enhanced TFT performance through the SAM treatment clearly demonstrates that the pV3D3 with SiOx capping layer can be a versatile surface modification platform. Furthermore, the achieved controllability of the surface composition of the pV3D3 layer without damaging the ultrathin dielectric layer is also essential for an optimal design of interface tailored to the semiconductors. Consequently, all OTFTs mentioned above operated with low voltage under 5 V thanks to the ultrathin gate dielectric layer. Coupled with a great advantageous characteristics of ultrathin pV3D3 dielectrics, the simple surface treatment method can be a breakthrough for next-generation electronic devices.

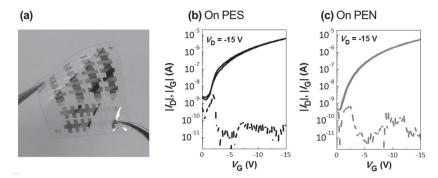

To fully utilize the merits of flexible gate dielectric layer as described in Figure 3c, flexible pentacene TFTs were demonstrated on polyethersulfone (PES) and PEN substrate, as shown in **Figure 7**. Here,  $O_2$  plasma-treated 40 nm thick pV3D3 was used as a dielectric layer. HMDS was treated on the capping layer. The pentacene TFTs on flexible substrates showed analogous device performance with the devices on rigid substrates. The flexible devices exhibited  $V_{\rm T}$  of lower than -1 V,  $\mu_{\rm FET}$  up to 0.45 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and low gate leakage current ( $I_{\rm G}$ ) of lower than  $10^{-9}$  A. The surface oxidization of the pV3D3 did not

**Figure 7.** Pentacene TFTs on flexible substrates fabricated with HMDS-treated pV3D3 as a dielectric layer: a) digital camera image of TFTs on PES, transfer characteristics of TFTs b) on PES, and c) on PEN.

damage both of dielectric layer and flexible substrate, confirming that the proposed system will enable to design flexible OTFT devices onto various kind of unconventional substrates.

### 3. Conclusion

In this study, a surface oxide layer was formed on the ultrathin pV3D3 using brief O<sub>2</sub> plasma treatment. On the pV3D3 with SiO<sub>x</sub> capping layer, further surface modification could be achieved by use of various silicon-based coupling agents including HMDS, OTS, and PFTS, without compromising the excellent insulating property of 15 nm thick pV3D3 layer. The top SiO<sub>x</sub> capping layer could also substantially enhance the thermal stability of pV3D3 dielectric, especially in air ambient, which is critically important to ensure the fabrication of reliable TFTs and further development of air-stable electronics including the devices for sensor applications. The TFTs with the surface-modified pV3D3 gate dielectric layer showed improved on-off ratio, and higher mobility compared to the untreated control device. The improved TFT performance is well consistent with the previous reports on the SAM-modified SiO<sub>2</sub> dielectric layer. Moreover, unlike the brittle inorganic dielectric layer, the ultrathin pV3D3 layer was fully compatible with various kinds of flexible substrates, thanks to the low process temperature of iCVD. Coupled with the excellent insulating property of the ultrathin pV3D3, the surface treatment method can be a powerful tool for further application to future flexible and wearable electronics.

### 4. Experimental Section

Substrates and Materials Preparation: All devices used in this work were fabricated on Eagle XG glass (Samsung Corning Co.) unless mentioned. Flexible TFTs were fabricated on polyethersulfone (PES, SKC Co.) and polyethylene naphthalate (PEN, Hanwha Chem.) Glasses were cleaned with ultrasonication in DI water, acetone, and isopropyl alcohol for 20 min then were dried with  $N_2$  blowing. For PES and PEN, same cleaning steps were applied without acetone. All the chemicals used in this work were purchased from Aldrich and used as received without further purification, unless mentioned otherwise.

Depositing Poly(1,3,5-trimethyl-1,3,5-trivinyl cyclotrisiloxane) (pV3D3) via the Initiated Chemical Vapor Deposition (iCVD): 1,3,5-trimethyl-1,3,5-trivinyl cyclotrisiloxane (V3D3, Gelest, 95%) and tert-butyl peroxide

www.afm-iournal.de www.MaterialsViews.com

(TBPO) were vaporized and delivered to the iCVD reactor, which is described elsewhere. The flow rates of V3D3 and TBPO were controlled by needle valve to 2.5 and 1 sccm, respectively. The process pressure was maintained at 300 mTorr, and the filament was heated to 200 °C. Substrate temperature was maintained at 40 °C. The thickness of the deposited polymer film was controlled in situ by the interferometer.

Surface Oxidation of Organosilicon Polymer Dielectrics and SAM Surface Treatment: The surface of iCVD polymer film was briefly treated with O2 plasma at 50 W for 15 s at the pressure of under 10<sup>-2</sup> Torr. The flow rate of O<sub>2</sub> during the plasma treatment was maintained at 25 sccm. To modify the oxidized surface of polymer, hexamethyldisilazane (HMDS, 99.9%, Aldrich) and trichloro (1H,1H,2H,2H-perfluorooctyl) silane (PFTS, 97%, Aldrich) was spin-coated onto the substrate at 3000 rpm for 35 s. Then, the HMDS-coated and PFTS-coated substrates were annealed on a hot plate at 150 °C for 30 min and 120 min, respectively. In the case of octadecyltrimethoxysilane (OTS, 90%, Aldrich), substrates were dip coated in pure OTS for 15 s then gently washed with acetone. For the OTS-coated substrates, same annealing procedure with HMDS-coated substrates was followed.

TFT Fabrication: 50 nm thick Al for gate electrode was deposited onto Eagle XG glass by thermal evaporation with the deposition rate of 1.5 Å s<sup>-1</sup>. Then, pV3D3 dielectric layer was deposited by iCVD process to the desired thickness. A SAM surface treatment was applied onto the iCVD-deposited pV3D3 layer, if necessary. On top of this layer, 50 nm of pentacene (TCI, 99.99% with sublimated grade) was thermally deposited at the base pressure of lower than  $10^{-6}$  Torr. The deposition rate of pentacene was  $0.5 \text{ Å s}^{-1}$ . For the source and drain (S/D) electrodes, WO<sub>3</sub> (20 nm)/Al (30 nm) was thermally evaporated consecutively through shadow mask, producing a channel dimension of 250  $\mu$ m (L)  $\times$  1000  $\mu$ m (W). The base pressure for the metal layer deposition was lower than 10<sup>-5</sup> Torr. All the TFT fabrication procedure was performed in a N<sub>2</sub>-filled glove box.

Thin Film Characterization: The chemical bonds in as-deposited and thermally annealed pV3D3 films were characterized by ALPHA Fourier transform infrared (FTIR) spectrometer (Bruker, Billerica MA). Thermogravimetric data of pV3D3 film was obtained from thermogravimetric analyzer (Setsys 16/18, Setaram). The surface morphology of as-deposited pV3D3, surface-modified pV3D3, and pentacene grains were monitored with AFM (PSIA). Contact angle of the surfaces was obtained from contact angle measurement system (Phoenix Series, S. E. O. Co. Ltd.). XPS (Thermo VG scientific) analysis was also conducted to assess the surface chemical composition of the surfaces. To test the flexibility of pV3D3 and SiOx/pV3D3, MIM devices prepared on 100 µm thick PEN substrates in the configuration of Al (50 nm)/insulator (30 nm)/Al (50 nm) devices were bended to the direction of tensile stress. The lowest bending radius (R) for the measurement was 1.5 mm, which corresponds to a tensile strain (S) of 3.3%. The strain could be calculated from the equation below;  $S = d_{sub}/(2R + d_{sub})$ where  $d_{\text{sub}}$  is the thickness of a substrate.

TFT Characterization: Capacitance (C<sub>i</sub>) of the TFT was obtained from MIM structure with the dimension of 1 mm imes 1 mm. All electrical characteristics were measured with Agilent B1500A semiconductor device analyzer. Mobility of the devices was extracted from the transconductance (g<sub>m</sub>);  $dg_m/dV_D = WL^{-1}C_i\mu$  where  $g_m=\partial I_D/\partial V_C/_{VD}$ .

### **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

## Acknowledgements

This work was supported by Samsung Research Funding Center of Samsung Electronics under Project Number SRFC-MA1402-00.

> Received: March 10, 2015 Revised: May 11, 2015 Published online: June 10, 2015

- [1] C. D. Dimitrakopoulos, P. R. L. Malenfant, Adv. Mater. 2002, 14, 99.

- [2] H. Klauk, Chem. Soc. Rev. 2010, 39, 2643.

- [3] A. Facchetti, M. H. Yoon, T. J. Marks, Adv. Mater. 2005, 17, 1705.

- [4] R. P. Ortiz, A. Facchetti, T. J. Marks, Chem. Rev. 2010, 110, 205

- [5] H. Klauk, M. Halik, U. Zschieschang, G. Schmid, W. Radlik, W. Weber, J. Appl. Phys. 2002, 92, 5259.

- [6] X. Y. Cheng, M. Caironi, Y. Y. Noh, J. P. Wang, C. Newman, H. Yan, A. Facchetti, H. Sirringhaus, Chem. Mater. 2010, 22, 1559.

- [7] X. H. Zhang, B. Domercq, B. Kippelen, Appl. Phys. Lett. 2007, 91,

- [8] J. Y. Kim, M. H. Yi, T. Ahn, Thin Solid Films 2010, 518, 6280.

- [9] A. A. Virkar, S. Mannsfeld, Z. A. Bao, N. Stingelin, Adv. Mater. 2010, 22, 3857.

- [10] L. Miozzo, A. Yassar, G. Horowitz, J. Mater. Chem. 2010, 20, 2513.

- [11] H. C. Yang, S. H. Kim, L. Yang, S. Y. Yang, C. E. Park, Adv. Mater. **2007**. 19. 2868.

- [12] H. Moon, H. Seong, W. C. Shin, W.-T. Park, M. Kim, S. Lee, J. H. Bong, Y.-Y. Noh, B. J. Cho, S. Yoo, S. G. Im, Nat. Mater. 2015,

- [13] M. E. Alf, A. Asatekin, M. C. Barr, S. H. Baxamusa, H. Chelawat, G. Ozaydin-Ince, C. D. Petruczok, R. Sreenivasan, W. E. Tenhaeff, N. J. Trujillo, S. Vaddiraju, J. J. Xu, K. K. Gleason, Adv. Mater. 2010, 22, 1993.

- [14] a) N. Bowden, W. T. S. Huck, K. E. Paul, G. M. Whitesides, Appl. Phys. Lett. 1999, 75, 2557; b) K. Efimenko, M. Rackaitis, E. Manias, A. Vaziri, L. Mahadevan, J. Genzer, Nat. Mater. 2005, 4, 293.

- [15] M. Kaltenbrunner, T. Sekitani, J. Reeder, T. Yokota, K. Kuribara, T. Tokuhara, M. Drack, R. Schwodiauer, I. Graz, S. Bauer-Gogonea, S. Bauer, T. Someya, Nature 2013, 499, 458.

- [16] D. K. Aswal, S. Lenfant, D. Guerin, J. V. Yakhmi, D. Vuillaume, Anal. Chim. Acta 2006, 568, 84.

- [17] A. Virkar, S. Mannsfeld, J. H. Oh, M. F. Toney, Y. H. Tan, G. Y. Liu, J. C. Scott, R. Miller, Z. Bao, Adv. Funct. Mater. 2009, 19, 1962.

- [18] S. Kobayashi, T. Nishikawa, T. Takenobu, S. Mori, T. Shimoda, T. Mitani, H. Shimotani, N. Yoshimoto, S. Ogawa, Y. Iwasa, Nat. Mater. 2004, 3, 317.

- [19] Y. D. Park, J. A. Lim, H. S. Lee, K. Cho, Mater. Today 2007, 10, 46.

- [20] a) R. Alfonsetti, L. Lozzi, M. Passacantando, P. Picozzi, S. Santucci, Appl. Surf. Sci. 1993, 70-1, 222; b) H. Hillborg, J. F. Ankner, U. W. Gedde, G. D. Smith, H. K. Yasuda, K. Wikstrom, Polymer 2000. 41. 6851.

- [21] S. G. Im, P. J. Yoo, P. T. Hammond, K. K. Gleason, Adv. Mater. 2007, 19, 2863.

- [22] J. Y. Park, H. Y. Chae, C. H. Chung, S. J. Sim, J. Park, H. H. Lee, P. J. Yoo, Soft Matter 2010, 6, 677.

- S. M. Gates, D. A. Neumayer, M. H. Sherwood, A. Grill, X. Wang, M. Sankarapandian, J. Appl. Phys. 2007, 101, 094103.

- [24] A. Grill, D. A. Neumayer, J. Appl. Phys. 2003, 94, 6697.

- [25] a) N. J. Trujillo, Q. G. Wu, K. K. Gleason, Adv. Funct. Mater. 2010, 20, 607; b) X. J. Chen, Y. D. Cui, G. Q. Yin, L. W. Liao, J. Appl. Polym. Sci. 2010, 117, 926.

- [26] D. D. Burkey, K. K. Gleason, J. Electrochem. Soc. 2004, 151, F105.

- [27] J. G. Laquindanum, H. E. Katz, A. Dodabalapur, A. J. Lovinger, J. Am. Chem. Soc. 1996, 118, 11331.

- [28] H. C. Yang, T. J. Shin, M. M. Ling, K. Cho, C. Y. Ryu, Z. N. Bao, J. Am. Chem. Soc. 2005, 127, 11542.

- [29] G. Horowitz, M. E. Hajlaoui, Synth. Met. 2001, 122, 185.

- [30] S. Y. Yang, K. Shin, C. E. Park, Adv. Funct. Mater. 2005, 15,

- [31] K. P. Pernstich, S. Haas, D. Oberhoff, C. Goldmann, D. J. Gundlach, B. Batlogg, A. N. Rashid, G. Schitter, J. Appl. Phys. 2004, 96, 6431.